A | B | C | D | E | F | G | H | CH | I | J | K | L | M | N | O | P | Q | R | S | T | U | V | W | X | Y | Z | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9

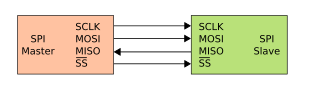

Serial Peripheral Interface (skratka SPI) je synchrónne sériové periférne rozhranie, primárne využívané v rámci vstavaných systémov pre komunikáciu na krátke vzdialenosti medzi riadiacimi mikrokontrolérmi a ostatnými integrovanými obvodmi resp. modulmi (EEPROM, A/D prevodníky, pamäťové karty, displeje, a pod.). Vyvinuté bolo na prelome 70. a 80. rokov 20. storočia spoločnosťou Motorola a v krátkom čase sa stalo de facto štandardom. Obojsmerná full-duplex komunikácia prebieha na spoločnej zbernici, adresácia obvodov je riešená prostredníctvom samostatných vodičov, ktoré zmenou stavu na logickú nulu aktivujú príjem a vysielanie zvoleného zariadenia (vývody SS alebo CS).[1]

Role zariadení na zbernici

- Master

- riadi časovanie prenášaných dát generovaním hodinového signálu

- vyberá, s ktorým zariadením na zbernici bude komunikácia prebiehať pomocou signálu SS – Slave Select (niekedy CS – Chip Select)

- Slave

- prijíma/vysiela podľa hodinového signálu, pokiaľ je aktivovaný pomocou SS/CS

Priebeh komunikácie

- Master nastaví log. 0 na SS zariadenia, s ktorým chce komunikovať.

- Následne začne generovať hodinový signál na SCLK v ktorého takte vyšlú obe zariadenia svoje dáta, pričom MOSI (Master Out, Slave In) vývody zariadení figurujú ako výstup na strane Mastra a vstup na strane Slave a MISO (Master In, Slave Out) naopak ako vstup na strane Mastra a výstup na strane Slave.

- Akonáhle sú dáta odoslané, môže komunikácia buď ďalej pokračovať (Master ďalej dodáva hodinový signál, hodnota SS sa nemení) alebo skončiť (Master prestane generovať hodinový signál a vráti SS na log. 1).

- Dĺžka prenášaných dát je typicky buď 8 bitov (bajt) alebo celočíselný násobok 8 bitov.

Polarita, fáza a frekvencia hodinového signálu

Vzťah medzi hodinovým signálom a dátami sa určuje dvomi konfiguračnými bitmi, ktoré sa v pôvodnej dokumentácii k SPI označujú ako CPOL a CPHA. Túto konvenciu definuje firma Freescale Semiconductor (pôvodne Motorola) v dokumente „SPI Block Guide“.[2]

- CPOL = 0; pokojová úroveň hodinového signálu je log. 0

- CPOL = 1; pokojová úroveň hodinového signálu je log. 1

- CPHA = 0; vysielajúci mení hodnotu pri zostupnej hrane (predošlého cyklu), prijímajúci číta hodnotu pri nábehovej hrane hodinového signálu

- CPHA = 1; vysielajúci mení hodnotu pri nábehovej hrane, prijímajúci číta hodnotu pri zostupnej hrane hodinového signálu

Niektoré logické analyzátory, vývojové nástroje alebo katalógové listy súčiastok používajú namiesto samostatných CPOL a CPHA príznakov číselný režim (Mode) podľa nasledovnej tabuľky:

| Mode | CPOL | CPHA |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

Maximálna frekvencia hodinového signálu, určujúca dátovú priepustnosť zbernice, závisí od limitov komunikujúcich obvodov, zvlášť Slave zariadení (Master môže pre komunikáciu s jednotlivými Slave zariadeniami používať rôzne hodinové takty). Limity sú spravidla uvedené v katalógových listoch obvodov a bývajú v praxi v rádoch jednotiek až desiatok MHz, existujú však aj periférie umožňujúce hodinové takty SPI do 100 MHz.[3]

Referencie

- ↑ Introduction to I²C and SPI protocols . byteparadigm.com, . Dostupné online.

- ↑ SPI Block Guide V03.06 . Motorola, 2003, . Dostupné online.

- ↑ LTC2376-20 : 20-Bit, 250ksps, Low Power SAR ADC . Analog Devices, . Kapitola ADC timing characteristics, s. 5. Dostupné online.

Pozri aj

- I²C – konkurenčný štandard spoločnosti Philips

Iné projekty

Commons ponúka multimediálne súbory na tému Serial Peripheral Interface

Commons ponúka multimediálne súbory na tému Serial Peripheral Interface

Externé odkazy

- Externí sériové sběrnice SPI a I²C – článok Pavla Tišňovského na serveri Root.cz (2008)

Zdroj

Tento článok je čiastočný alebo úplný preklad článkov Serial Peripheral Interface na českej Wikipédii a Serial Peripheral Interface na anglickej Wikipédii.

Text je dostupný za podmienok Creative Commons Attribution/Share-Alike License 3.0 Unported; prípadne za ďalších podmienok. Podrobnejšie informácie nájdete na stránke Podmienky použitia.

Antropológia

Aplikované vedy

Bibliometria

Dejiny vedy

Encyklopédie

Filozofia vedy

Forenzné vedy

Humanitné vedy

Knižničná veda

Kryogenika

Kryptológia

Kulturológia

Literárna veda

Medzidisciplinárne oblasti

Metódy kvantitatívnej analýzy

Metavedy

Metodika

Text je dostupný za podmienok Creative

Commons Attribution/Share-Alike License 3.0 Unported; prípadne za ďalších

podmienok.

Podrobnejšie informácie nájdete na stránke Podmienky

použitia.

www.astronomia.sk | www.biologia.sk | www.botanika.sk | www.dejiny.sk | www.economy.sk | www.elektrotechnika.sk | www.estetika.sk | www.farmakologia.sk | www.filozofia.sk | Fyzika | www.futurologia.sk | www.genetika.sk | www.chemia.sk | www.lingvistika.sk | www.politologia.sk | www.psychologia.sk | www.sexuologia.sk | www.sociologia.sk | www.veda.sk I www.zoologia.sk