A | B | C | D | E | F | G | H | CH | I | J | K | L | M | N | O | P | Q | R | S | T | U | V | W | X | Y | Z | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9

Complementary Metal Oxide Semiconductor , skr. CMOS, je technológia výroby logických integrovaných obvodov (čipov).

Najcharakteristickejšou vlastnosťou obvodov vyrobených touto technológiou je takmer nulový prúd pretekajúci obvodom v statickom stave, t. j. keď sa logické úrovne na vstupoch (a tým aj výstupoch) nemenia. Prúd CMOS obvod odoberá len pri prepínaní.

Preto sú CMOS čipy obvody mnohonásobne úspornejšie ako čipy vyrobené staršou technológiou NMOS či technológiami založenými na bipolárnych tranzistoroch. Prakticky všetky logické integrované obvody sú dnes vyrábané technológiou CMOS.

Návrh

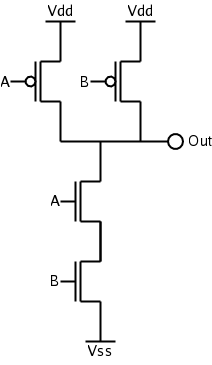

Pri realizácii logickej funkcie (či už jednoduchej alebo zložitej) sa obvod skladá z dvoch častí:

- NMOS časť, pripínajúca výstup do nuly ale izolujúca po prepnutí do log1

- PMOS časť, pripínajúca výstup do log1 (ale izoluje od log0)

Každá táto časť je logickou negáciou druhej.

Šírka kanálu (w) pre PMOS je väčšinou 2 krát väčšia ako šírka kanálu pre NMOS pre logické obvody.

Technická realizácia

Základné prvky sú odvodené od klasických PMOS a NMOS, len hradlá sú aj napriek M v skratke MOS z tepelne odolnejšieho a lacnejšieho polykryštalického kremíka. V rámci výskumu sa však experimentuje aj s kovovými elektródami.

Obvody rady 4000 operujú s TTL úrovňou, ale v počítačoch sa prešlo na nižšie napätia, pretože to znižuje výkonový rozptyl (laterálne skraty cez parazitné kapacity) pri vysokých frekvenciách. Typické napätia sú 3,3V alebo 1,8V a pri supervysokých frekvenciách sú aj menšie ako volt. Niektoré čipy pre niektoré rozhrania majú interne nízke napätia a dovonka TTL.

Krátko povedané, frekvencia sa dá zvýšiť vďaka zmenšeniu napätia, takže je ohraničená len latenciou. Ale vďaka nižším napätiam sa dá aj čipová štruktúra zmenšiť tenšími izolačnými vrstvami (menší čip ⇒ menšia latencia) bez rizika prierazu a signálových „duchov“ .

Text je dostupný za podmienok Creative Commons Attribution/Share-Alike License 3.0 Unported; prípadne za ďalších podmienok. Podrobnejšie informácie nájdete na stránke Podmienky použitia.

Antropológia

Aplikované vedy

Bibliometria

Dejiny vedy

Encyklopédie

Filozofia vedy

Forenzné vedy

Humanitné vedy

Knižničná veda

Kryogenika

Kryptológia

Kulturológia

Literárna veda

Medzidisciplinárne oblasti

Metódy kvantitatívnej analýzy

Metavedy

Metodika

Text je dostupný za podmienok Creative

Commons Attribution/Share-Alike License 3.0 Unported; prípadne za ďalších

podmienok.

Podrobnejšie informácie nájdete na stránke Podmienky

použitia.

www.astronomia.sk | www.biologia.sk | www.botanika.sk | www.dejiny.sk | www.economy.sk | www.elektrotechnika.sk | www.estetika.sk | www.farmakologia.sk | www.filozofia.sk | Fyzika | www.futurologia.sk | www.genetika.sk | www.chemia.sk | www.lingvistika.sk | www.politologia.sk | www.psychologia.sk | www.sexuologia.sk | www.sociologia.sk | www.veda.sk I www.zoologia.sk