A | B | C | D | E | F | G | H | CH | I | J | K | L | M | N | O | P | Q | R | S | T | U | V | W | X | Y | Z | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9

| General information | |

|---|---|

| Launched | 1994 |

| Discontinued | current |

| Common manufacturer(s) |

|

| Performance | |

| Max. CPU clock rate | 32 kHz to 320 MHz |

| Data width | 32 |

| Address width | 32 |

| Cache | |

| L1 cache | configurable |

| Architecture and classification | |

| Application | Embedded, Mobile equipment, Air conditioner, Automotive |

| Technology node | 0.8 μm to 40 nm |

| Microarchitecture | V810 (1991), V850 (1994), V850E (1996), V850E1 (1999), V850ES (2002), V850E2 (2004), V850E1F (2005), V850E2v2 (FIX ME), V850E2v3 (2009), V850E2v4 (2010), V850E2v3S (2011), V850E3v5 (2014) |

| Instruction set | V800 Series |

| Extensions |

|

| Number of instructions | v850: 74 v850e: 81 v850e1: 80 (83) v850e1f: 96 v850e2: 89 v850e2v3: 98 V850e3v5: FIX ME |

| Physical specifications | |

| Cores |

|

| Products, models, variants | |

| Product code name(s) |

|

| Variant(s) |

|

| History | |

| Predecessor(s) | "V80" CISC core |

V850 is a 32-bit RISC CPU architecture produced by Renesas Electronics for embedded microcontrollers. It was designed by NEC as a replacement for their earlier NEC V60 family, and was introduced shortly before NEC sold their designs to Renesas in the early 1990s. It has continued to be developed by Renesas as of 2018[update].

The V850 architecture is a load/store architecture with 32 32-bit general-purpose registers. It features a compressed instruction set with the most frequently used instructions mapped onto 16-bit half-words.

Intended for use in ultra-low power consumption systems, such as those using 0.5 mW/MIPS, the V850 has been widely used in a variety of applications, including optical disk drives, hard disk drives, mobile phones, car audio, and inverter compressors for air conditioners. Today, microarchitectures primarily focus on high performance and high reliability, such as the dual-lockstep redundant mechanism for the automotive industry; and the V850 and RH850 families are comprehensively used in cars.

The V850/RH850 microcontrollers are also used prominently on non-Japanese automobile marques such as Chevrolet, Chrysler, Dodge, Ford, Hyundai, Jeep, Kia, Opel, Range Rover, Renault and Volkswagen Group brands.

Overview

The V850 is the trademark name for a 32-bit RISC CPU architecture for embedded microcontrollers of Renesas Electronics Corporation. It was originally developed and manufactured by NEC Corporation in the early 1990s[1][2] (the copyright mark for the microcode on the package shows 1991) as a branch of the V800 Series[3]: 97, PDF103 and is still being evolved today.[4]

Its base-architecture has been succeeded by the V850 family variants, named V850E, V850E1, V850ES,[5] V850E1F, V850E2, V850E2M, V850E2S, and the RH850 family (V850E2M, V850E2S, and V850E3) CPU cores.

Many compilers and debuggers are available from various development tool vendors.

Real-time operating systems are provided by compiler vendors.

In-circuit emulators (ICE) are provided by many vendors. Legacy proven pod-based types—the JTAG-based N-Wire interface with the N-trace type, and the Nexus interface with the Aurora Trace type—are available.

Application systems

The first V850 CPU core was used in many DVD drives manufactured by NEC's and Sony's Optiarc (later wholly owned by Sony).[6][7] NEC Electronics (currently Renesas Electronics) itself intensively developed application-specific standard products (ASSPs) for SCOMBO Series optical disk drives.[8][9] This first generation of processor core was also used for hard disk drives manufactured by Quantum Corporation (see photo).

In 1997, the V850/xxn product line started with the V850/SA1[10] and the V850/SV1[11] and expanded its application to ultra-lo-power products such as "handy camcorders." It has a main and sub internal oscillator amplifier working from 1.8 V to 3.6 V with external crystal or ceramic resonator.[10] Software STOP mode, whose internal watch timer operates with a 32.768 kHz sub-oscillator, typically consumes only 8μA of electrical current.[12][13] In 1998, NEC launched the V850/SB1,[14] with IEBus controller, for car audio, an ultra-low-power (3.6 mW@5 V/MIPS) and ultra-low-noise (EMI/EMS) 5 V product.[15] The V850/SC1[16] was also for car audio.[17] These strategic product line expansions succeeded in increasing the number of devices sold.

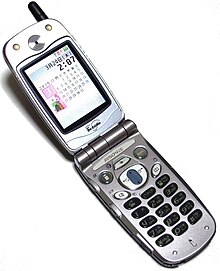

This first generation of the V850 core is also used for some NEC mobile phones.[18] It is also used for the programmable-host CPUs of some small form factor GSM/GPRS mobile devices with GPS embedded modem modules.[19]

In the next phase, NEC targeted the automotive industry with a CAN bus controller based on the V850,[20] as the V850/SF1.[21] Later on, the automotive industry became the main target of the V850 and RH850.

The V850E core was targeted at system-on-a-chip (SoC) applications as well as standard products,[22][23] and was used for some Japanese domestic mobile phones, including Sony Mobile's and NEC's.[24][25][26][27][28] V850E and V850ES are also used in air conditioning inverter compressors.[29][30][31][32] At this stage, another mass market was its use in car audio.[33] The V850ES core succeeded in the low-power embedded-product line,[34] and is ISA-compatible with the V850E. NEC Electronics (currently, Renesas Electronics) adopted the V850 CPU core for its USB 3.0 controllers.[35]: 11

Around 2005, several companies started a feasibility study for the FlexRay controller on the V850E platform. Yokogawa Digital Computer (currently DTS INSIGHT) developed an evaluation board named GT200 with a V850E/IA1 and a field-programmable gate array (FPGA), which employs the FlexRay controller developed by Bosch.[36]: 78, PDF80

The V850E2 core primarily targeted automotive areas,[37] but was also used for NEC's mobile phones.[38]

The V850 family line up (based on V850E, V850ES, and V850E2 cores) and the Renesas RH850 family (based on the V850E3 core, as of 2018) are mainly employed in automotive applications as well as inter-equipment connectivity and motor-control specific microcontroller units (MCUs).[39][40]

Trademark strategy

The V850 is a unregistered trademark but not a registered one.[41] NEC once applied for a trademark to be registered with the Japan Patent Office, but it was rejected,[42][43] as it was a natural extension of the series number. However, this action has been enough to prevent other people or organizations from registering it as a trademark. In addition, Renesas has been using the V850X/xxn type trademark, such as V850E/MA1, for more than 20 years, because the combination of one alphabetical with two numerical characters cannot be granted as a registered trademark. It is thus free to use without registration.

One exception is V850E/PHO3 (PHOENIX 3, or PHOENIX-FS).[44]: 3 [45]: 33 Another usage of PHOENIX 3 by Renesas Electronics is the COOL PHOENIX 3, which employs the ARM Cortex-M0 core.[46] PHOENIX 3 is a registered trademark of the 3DO Company as USPTO Reg. 2,009,119.[47]

According to current Renesas Electronics documentation, at least the following strings are regarded as its trademark: "V800 Series", "V850 family", "V850/SA1", "V850/SB1", "V850/SB2", "V850/SF1", "V850/SV1", "V850E/MA1", "V850E/MA2", "V850E/IA1", "V850E/IA2", "V850E/MS1", "V850E/MS2", "V851", "V852", "V853", "V854", "V850", "V850E", and "V850ES".[41][48]

Because the V850 trademark has been used for more than 20 years, most people do not know that the RH850 family is based on an extension of the V850 instruction set architecture, and has backward compatibility with V850, V850E, V850ES, and V850E2. The RH850 is consequently thought of as being without the legacy software compatibility of the V850.[49][50]

Development methodology

Marked as "©NEC 1991."

Because the V850 family[48]: 16 was developed as a branch of the V800 series,[3]: 97, PDF103 the basic CPU architecture is inherited from the V810.[52] The instruction set architecture of the first V850 is drastically modified from that of the V810, but the difference is within a patch level from the GNU Compiler Collection point of view.[53] The main purpose of this change is to implement saturation arithmetic at customers' request.

The detailed design methodology of the V810 is described in this journal.[54] The V850 utilizes these design assets; but the datapath logic was changed from dynamic logic to static logic, to enable 32.768 kHz real-time clock frequency operation mode.

The register-transfer level "CPU architecture design" of the V810 is developed with the Functional Description Language (FDL)[55][56][57] on the Falcon Simulator software, which are NEC's in-house CAD tools. This methodology is the same as that used for the NEC V60.[58] In the late 1980s, the Verilog HDL had not yet been acquired by Cadence Design Systems.[59] FDL had been used until the middle of the 2000s, and was also used for the development of NEC's super-computer named Earth Simulator.[60]

The difference from V60 is that the circuit diagram was written with a schematic editor, not of Calma but of Mentor Graphics, called NETED,[61] a part of the Design Architect product[62][63] on Apollo Computer's workstation, which was the major schematic editor at that moment.[64] It enabled designers to generate netlists, such as EDIF and SPICE, for LVS programs like cadence's Dracula products, and NEC's in-house Zycad netlist for logic simulation. Later on, this circuit diagram of NETED was able to generate a gate-level Verilog HDL netlist for V850.

Most of the register-transfer-level FDL netlist was translated to the gate-level schematic by hand, because the logic synthesis had not yet to be practical. The FDL was precisely divided into datapath and random logic. For the datapath part, the gate-level circuit diagram enabled manually repeated artwork. On the other hand, for the random logic part, logic synthesis was tried for generating gate-level schematic, but it was only about 10% of the total circuit.

In addition, formal verification was also not yet practical, which meant that full regression test by dynamic logic simulation was required for the gate-level netlist to compare with the RTL one. For gate-level logic simulation, NEC's in-house CAD tool V-SIM was usually used.[65] But sometimes a hardware emulator, such as Zycad LE simulation accelerator,[66] was used for this purpose. (Refer to:.[67]: 13 In this material, the performance of Zycad LE is compared with NEC's HAL, but initial design decade differs.[68])

Architecture

Basic architecture

The basis of the V810 and V850 has a typical general-purpose registers-based load/store architecture.[69]: 4

There are 32 32-bit general-purpose registers. Register 0 (R0) is fixed as the Zero Register which always contains zero.

In the V850, R30 is implicitly used by the sld and sst instructions. 16-bit short-format load/store instructions use element pointer (ep), where the addressing mode comprises the base address register ep and immediate-operand offsets.

In V850E or later microarchitectures, R3 is implicitly used by PREPARE/DISPOSE; call stack frame creation; and unwinding instructions, as a stack pointer. Compilers' calling conventions also use R3 as the stack pointer.

The original V850 has a simple 5-stage 1-clock pitch pipeline architecture.[48]: 114–126 This is a significant feature of reduced instruction set computers (RISCs). But the object-code size is about half that of the MIPS R3000,[69]: 5 because the V810 and V850 adopted 16-bit and 32-bit 2-way form-length instruction formats, respectively,[48]: 38–40 [69]: 17 [70]: 29–30 and most of the frequently used instructions are mapped onto a 16-bit half-word. In other words, a 16-bit external bus width is enough to provide instructions continuously without pipeline stalling, which enables low power consumption on the application board, and is suitable for mobile equipment. This concept is similar to Renesas (formerly, Hitachi) SH, ARM Thumb, and MIPS16 instruction set architectures.[71]: 4

In addition, the instruction set is carefully implemented. For example, to execute a function call with a Jump and (Register) Link instruction,[48]: 61 [69]: 20 [70]: 64 which saves the next program counter (PC) on a register (fixed to R31 in V810), is also one of the RISC techniques to reduce the number of instructions. Return from the function can be accoomplished by jmp (jmp in V810) instruction.[48]: 61 [69]: 23 [70]: 65 Typical CISC processors use call and return instructions and push the next PC on their stack memory area.

But V810 and V850 have some microarchitecture differences. The V810 adopts a microprogram operation method for some instructions, such as floating-point arithmetic and bit string operations, while the V850 uses a one-hundred-percent hardwired control method. As a result, for example, the first V850 does not have floating-point arithmetic and bit manipulation instruction sets, including the "find first one/zero" (search 1/0; SCH1x/SCH0x), except for "set/clr/negate a bit" (SET1/CLR1/NOT1). Those extended instruction sets are revived in V850E2x extensions.

Though the V800 series adopts a RISC instruction set architecture, their assembly language is hand-coding friendly. They adopt a straightforward load/store architecture.[69]: 4 In addition, the "interlock" mechanism, both for the data hazards and for the branch hazards, are implemented:[69]: 33–35 in other words, an assembly language programmer does not need to consider any delay slots. 32 general-purpose registers provide flexibility for assembly language users. A mixture of hand-assembled codes and C language compiled codes is facilitated by using compiler options, such as "-mno-app-regs" in the Gnu Compiler Collection.[72]

The IN instruction of the V810, which enables unsigned-load from memory-mapped I/O, was removed from the first V850s.[69]: 22 [70]: 63

Detailed discussions are available in some old journals.[73][74]

Instruction set extensions

The V850 series added many instruction set extensions, but all the extensions have backward compatibility.[75] Therefore, old binary software assets work on the new cores.

The first generation of the V850 does not have unsigned load instructions, which had been removed from the V810 (where it was implemented with IN.H and IN.B). Then, in the second generation V850E (V850E1) Series, such unsigned functionality was again added (with LD.HU and LD.BU). In addition, the V850E has some other user-friendly "CISCy" extensions, such as call table, switch, and prepare/dispose.[76]: 217

In 1996, the V853 was announced as the first 32-bit RISC microcontroller with integrated flash memory.[77] But its maximum number of "erase and write" cycles was 16.[78]: 37

In 1998, NEC strategically started to expand the V850 product line, to standard, application-specific_standard_product (ASSP), application-specific integrated circuit (ASIC), and system on a chip (SoC) businesses.[79]

In 2001, NEC launched V850ES core, which is an ultra-low-power series, but is ISA-compatible with the V850E.[80]

Around 2001, Java Acceleration IP core for the V850 seemed to be provided to some customers as SoC,[81] but detailed information is only found in some patents.[82][83]

In 2005, NEC Electronics introduced V850E2 core as the V850E2/ME3 product line with super-scalar architecture.[84]

In 2009, NEC Electronics introduced V850E2M as dual-core with 2.56MIPS/MHz and 1.5 mW/MIPS.[85]

In 2011, Renesas disclosed the SIMD extension for the V850 as V850E2H.[75][86] As for the SIMD extension, some academic studies were done.[87] But architectural documentation for this latest product line is disclosed to automotive customers only; it cannot be found on Renesas' website.[88] Its name seems to have been changed to V850E3 or G3H. The only way to know about its instruction set is to reverse engineer it with the GNU Compiler Collection.

Power consumption

The original V810 and V850 CPU architecture is designed for ultra-low power applications.

The V810 is described in detail in some journals.[89][90]

According to Renesas's documentation, the power consumption of the V850ES/Jx3-L implementation is about 70% of ARM Cortex-M3.[5]: 14, 15

The V810 was one of the most low-power 32-bit microcontroller products of the early 1990s. It operates at from 2.2 V to 5.5 V with a 5 V 0.8 μm (CZ4) fabrication process.[91] Measured with Dhrystone MIPS, power dissipation is 500 mW at 15MIPS and 40 mW at 6 MIPS, at 5 V and 2.2 V, respectively. This specification can be achieved both by well considered instruction-set architecture and by precisely tuned 5-stage 1-clock pitch pipeline microarchitecture, both of which are the benefit of a simplified RISC architecture.

This ultra-low-power architecture was succeeded by V850/Sxn product line, which are still being mass-produced after 20 years. Most of the improved chips are produced using a 3.3 V, 0.35μm (UC1) fabrication process, where the CPU core is precisely tuned to operate from 1.8 V to 3.6 V, working at 32.768 kHz (sub-oscillator) to 16.78 MHz (main-oscillator) with internal oscillator amplifier plus external resonator (crystal or ceramic).[10]

Its power dissipation is 2.7 mW/MIPS at 3.3 V when made with a 0.35 μm (UC1) fabrication process, and 3.6 mW/MIPS at 5 V with a 0.35 μm (CZ6) fabrication process. "Software STOP" stand-by mode for the mask ROM version of V850/SA1, whose internal watch timer operates at 3.3 V with 32.768 kHz sub-oscillator (IDD6), consumes typically only 8 μA electrical current. Subclock normal operation mode at 3.3 V with 32.768 kHz consumes 40 μA typically, 140 μA at the maximum. (IDD5)[92]: 440, IDD5 [13]

Its 1.8 V typical CPU operating current at 32.768 kHz might be 22 μA (40 μA ÷ 3.3 V × 1.8 V), where power dissipation should be 40 μW. It corresponds to 1.0 mW/MIPS (40 μW ÷ 0.032768 MHz ÷ 1.15 DMIPS/MHz ÷ 1000).

The V850/Sxn product line is also tuned for low noise, with both EMI and with EMS. The V850/SB1 and SB2 are especially tuned for low EMI noise with a 5 V internal voltage regulator, which facilitates high sensitivity in receiving RF for car radios.[93]: 41–44

In 2011, NEC launched the 3rd generation microarchitecture V850ES ultra-low-power series, which achieves 1.43 mW/MIPS at an operating voltage range of from 2.2 V to 2.7 V,[80] but this first implementation of V850ES microarchitecture seems to be incomplete compared with later generations of the same architecture. Its "Sub-IDLE" stand-by mode for the mask ROM version of V850ES/SA2 and V850ES/SA3, whose internal RTC operate at 2.5 V with 32.768 kHz sub-oscillator (IDD6), consume typically only 5 μA electrical current. But, Subclock normal operation mode at 2.5 V with 32.768 kHz consumes typically 40 μA, 100 μA at the maximum.[94]: 509 Its 2.2 V typical CPU operation current at 32.768 kHz might be 31 μA (40 μA ÷ 2.5 V × 2.2 V), where power dissipation should be 68 μW. This is about 1.7 times that of V850/SA1. It corresponds to 1.6 mW/MIPS (68 μW ÷ 0.032768 MHz ÷ 1.3 DMIPS/MHz ÷ 1000).

The V850ES/JG3-L product line has ultra-low-power variants, the μPD70F3792, 793, and the μPD70F3841, 842. They can operate from 2.0 V to 3.6 V with typical electrical current of 18 μA at 32.768 kHz,[95]: 1002, 1041 which should be 22 μW at 2.0 V (18 μA × 2.0 V ÷ 3.3 V × 2.0 V). This corresponds to 0.52 mW/MIPS (22 μW ÷ 0.032768 MHz ÷ 1.3 DMIPS/MHz ÷ 1000). In addition, their sub-clock idle mode power consumption, with watch timer, should be typically 3.4 μW at 1.8 V (3.5 μA ÷ 3.3 V × 1.8 V × 1.8 V).[95]: 1002, 1041

The power consumption of the NA85E2 (V850E2) core is much larger compared with the NU85E (V850E1) core using the same CB-12L (UX4L)[91][96] fabrication process. The reason is that the V850E2x core has a 128-bit instruction prefetch bus and more than one instruction prefetch queue,[97]: 16 while the average instruction length of the V800 series is 16 bits.[69]: 17 It means 16 instructions can be fetched from the memory at once, and the memory and prefetch circuits sleep fors 3 to 7 cycles for dual-pipeline superscalar architecture. This gap enlarges electrical current amplitude differences. In addition, the peak electric current exceeds allowances for the voltage stabilizers of mobile gadgets. As for V850E2M CPU core, it is publicly introduced as 1.5 mW/MIPS, 3 times that of former generations, although it should be able to take advantage of new fabrication process technologies.[85] Some mobile equipment avoids using dual-instruction execution (dual-pipeline superscalar), adopting the single-instruction (single-pipeline) execution setting to reduce electrical current amplitude differences.

Instruction opcode table

Each opcode (operation code) table is from User's Manual: Architecture (refer to external links.).

V810 (obsoleted)

- 1st map opcodes

- All opcodes (operation codes) of the hardwired control operation are contained within the first 16-bit half-word of an instruction, from the most significant bit (MSB). A 64-word depth ROM structure with branch condition code table is enough for decoding hardware. If a 16-bit literal operand is required, it is located in the second half-word. Microprogram control operations, bit strings, and floating-point arithmetic instructions are also located in the second 16-bit half-word. As a result, all the instructions have 16-bit and 32-bit 2-way form length. Unsigned load form memory mapped I/O is implemented as the

Ininstruction. Arithmetic and logical instructions are not fully, but relatively, orthogonal. - The V810 does not have saturation arithmetic instructions, but 1 additional instruction in format II, such as

SATwhich checks flags (Overflow,Sign,Zero, andHalf-word) and rewrites the specified register, might be enough both for signed and unsigned, and for word and half-word, arithmetic operations.

Bit

000 001 010 011 100 101 110 111 Format 000 X MOV ADD SUB CMP SHL SHR JMP SAR I(R,r) 001 X MUL DIV MULU DIVU OR AND XOR NOT 010 X MOV ADD SETF CMP SHL SHR SAR II(imm5,r) 011 X TRAP RETI HALT LDSR STSR Bit str.

100 0

100 1Bcond III(disp9) BV BZ/BE BN(BS) BLT BNV BNZ/BNE BP(BNS) BGE BC/BL BNH BR BLE BNC/BNL BH NOP BGT 101 X MOVEA ADDI JR JAL ORI ANDI XORI MOVHI IV/V 110 X LD.B LD.H LD.W ST.B ST.H ST.W VI(disp16,r) 111 X IN.B IN.H CAXI IN.W OUT.B OUT.H Float OUT.W VI/VII

NOPis an alias ofNon-BR.

V850 (1st Gen.)

- 1st map opcodes